# Esperimenti con TTL e 8080A

VOLUME 2 - ELETTRONICA DIGITALE, TECNICHE DI PROGRAMMAZIONE E INTERFACCIAMENTO DEI MICROCOMPUTER

**EDIZIONE ITALIANA**

PETER R. RONY GRUPPO EDITORIALE JACKSON

# Esperimenti con TTL e 8080A

VOLUME 2 - ELETTRONICA DIGITALE, TECNICHE DI PROGRAMMAZIONE E INTERFACCIAMENTO DEI MICROCOMPUTER

#### PETER R. RONY

Department of Chemical Engineering

Virginia Polytechnic Institute & State University

Blacksburg, Virginia 24061

GRUPPO EDITORIALE JACKSON Via Rosellini, 12 20124 Milano

© Copyright per l'edizione originale Peter R. Rony © Copyright per l'edizione italiana Gruppo Editoriale Jackson

Tutti i diritti sono riservati. Nessuna parte di questo libro può essere riprodotta, posta in sistemi di archiviazione, trasmessa in qualsiasi forma o mezzo, elettronico, meccanico, fotocopiatura, etc., senza autorizzazione scritta.

Terza edizione: 1981

Stampato in Italia da Stabilimento Grafico Matarelli S.p.A. - Via Antoine Watteau, 7 - 20125 MILANO

# INTRODUZIONE ALL'EDIZIONE ITALIANA

Questa trattazione, composta da due volumi, ha rappresentato negli Stati Uniti una pietra miliare nella divulgazione e nell'insegnamento dell'elettronica digitale e delle tecniche di utilizzo dei microprocessori.

I testi sono sorti da esperienze didattiche dell'autore, che svolge attività di ricercatore e docente presso il Virginia Polytechnic Institute and State University.

Questa esperienza scolastica ad alto livello è una delle caratteristiche più interessanti di questi due libri, che possono anche essere utilizzati come validi manuali di autoistruzione.

Nella preparazione dell'edizione italiana, abbiamo cercato il più possibile di mantenere lo stile colloquiale dell'autore, che del resto dal punto di vista umano è molto estroverso ed entusiasta della sua attività di ricercatore.

Abbiamo mantenuto molti termini tecnici inglesi sia per il diffuso utilizzo che se ne fa nella corrente terminologia elettronica, sia per familiarizzare il lettore con un certo linguaggio, che sempre più è presente nella letteratura tecnica.

Le apparecchiature descritte nei volumi e e utilizzate negli esperimenti, hanno avuto origine dall'attività di rierca dell'autore, secondo precise esigenze didattiche; queste apparecchiature sono prodotte dalla E-L Instruments.

Un particolare ringraziamento va a quanti hanno collaborato alla realizzazione della versione italiana di questi libri, l'Ing. Aldo Cavalcoli, l'Ing. Valerio Scibilia, l'Ing. Ettore Valsecchi, la Sig.na Daniela Fornari, la Sig.ra Rosaria Lucano, il Sig. Marcello Longhini, la Sig.ra Francesca Di Fiore, il Sig. Giampietro Zanga e il Sig. Paolo Reina.

Un ringraziamento va anche alla Microlem s.a.s. - Via C. Monteverdi, 5 - 20131 Milano - distributore per l'Italia delle apparecchiature della E-L Instruments - l'organizzazione che ha reso possibile e agevolato il nostro lavoro.

Siamo particolarmente grati anche a "La Scuola di Elettronica di Milano" che, utilizzando i nostri testi per i suoi apprezzatissimi corsi, svolge una continua e scrupolosa revisione.

Questa terza edizione, riveduta e corretta, è stata possibile grazie al lavoro svolto dalla succitata Scuola.

Gruppo Editoriale Jackson

# SOMMARIO

| INTRODUZIONE ALL'EDIZIONE                                                                                                                                                                                                                                                                                              | E ITALIANA                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| PREFAZIONE                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| CAPITOLO 16 - COSA VUOL D                                                                                                                                                                                                                                                                                              | IRE INTERFACCIARE?                                                                                                                     |

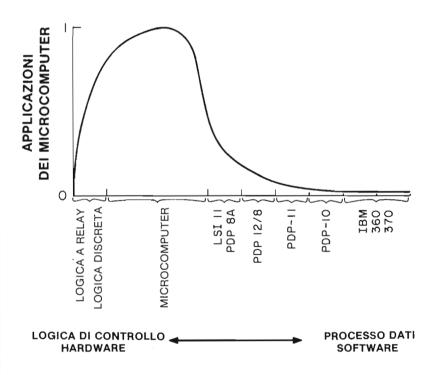

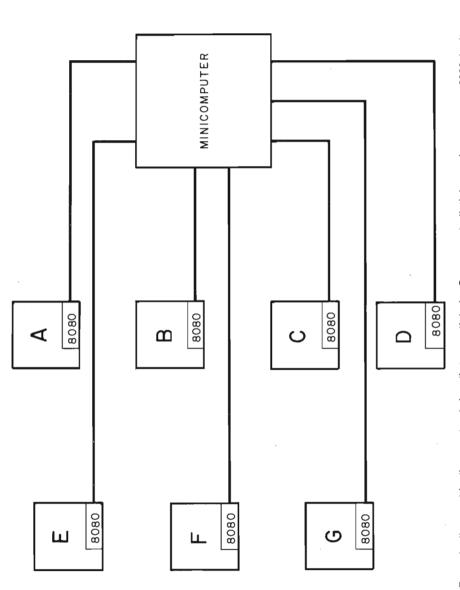

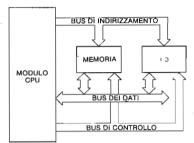

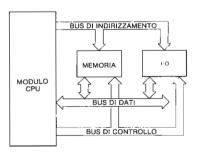

| Obiettivi La rivoluzione della mac Microprocessore e micro Hardware e software . Cosa è un controllore? Dove si collocano i micro Gerarchie di computer Un tipico microcomputer Bus di indirizzamento Data bus bidirezionale Bus di controllo Cosa vuol dire interfacci Cosa è un dispositivo di Domande riepilogative | 16-1 16-1 16-1 16-1 16-1 16-2 16-2 16-5 16-7 16-7 16-7 0computer 16-8 16-10 16-12 16-13 16-14 16-14 16-14 16-17 1/O? 16-19 16-20 16-21 |

| Obiettivi Che cosa è un impulso de La sostituzione dell'hardi dispositivo Uso degli impulsi di sele Come si generano gli im Istruzioni di ingresso/uso I cicli macchina fetch, in Primo programma Secondo programma                                                                                                    | 17-1                                                                                                                                   |

| Esperimento N. 2 Esperimento N. 3 Esperimento N. 4 Esperimento N. 5 Esperimento N. 6 Esperimento N. 7 Esperimento N. 8 Esperimento N. 9 Domande riepilogative                                                                                                                                                          | 17-23<br>17-25<br>17-25<br>17-30<br>17-35<br>17-40<br>17-44                                                                            |

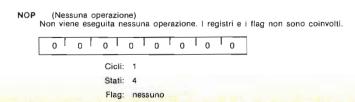

#### CAPITOLO 18 - IL SET DI ISTRUZIONI 8080A

|      | Introduzione                                                  |

|------|---------------------------------------------------------------|

|      | Obiettivi                                                     |

|      | Fonti d'informazione per la programmazione 8080               |

|      | Sommario del set di istruzioni dell'8080                      |

|      |                                                               |

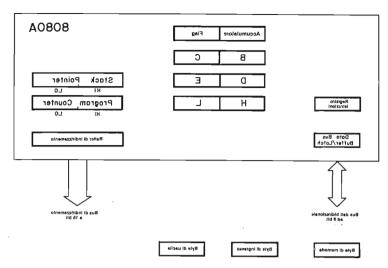

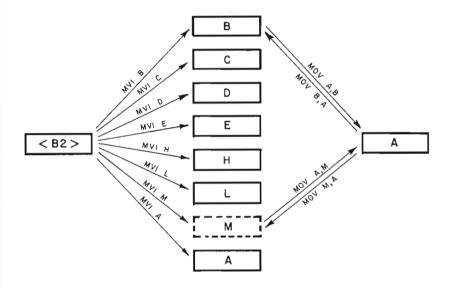

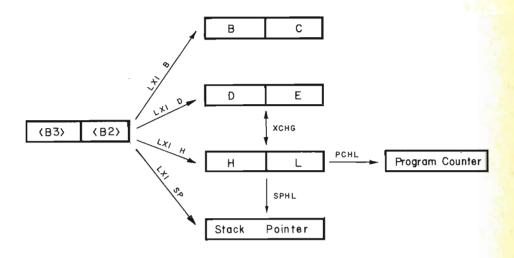

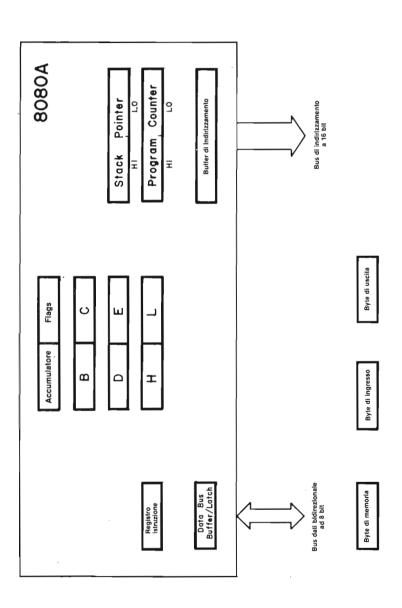

|      | I registri del microprocessore 8080                           |

|      | Che tipi di operazioni esegue il microprocessore 8080A? 18-10 |

|      | Codice mnemonico delle istruzioni dell'8080                   |

|      | Set di istruzioni                                             |

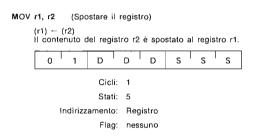

|      | Gruppo trasferimento dati                                     |

|      | Gruppo aritmetico                                             |

|      | Gruppo logico                                                 |

|      | Gruppo di salto                                               |

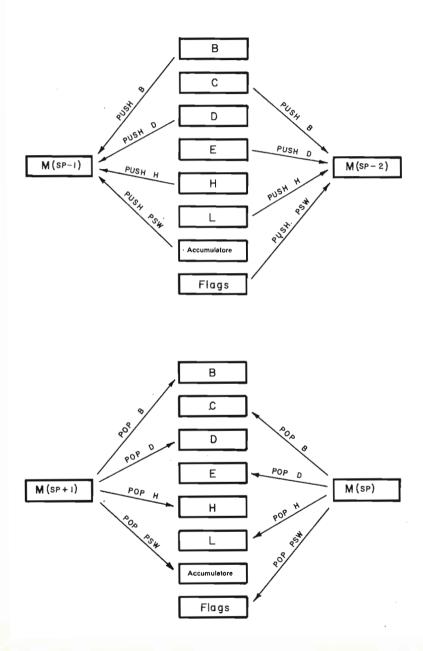

|      | Gruppo stack, I/O, controllo macchina                         |

|      | Introduzione agli esperimenti                                 |

|      | Esperimento N. 1                                              |

|      | Esperimento N. 2                                              |

|      | Esperimento N. 3                                              |

|      | Elenco ottale/esadecimale del set di istruzioni 8080          |

|      | Sommario del set di istruzioni 8080                           |

|      | Domande riepilogative                                         |

|      |                                                               |

|      | Risposte                                                      |

|      |                                                               |

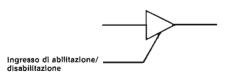

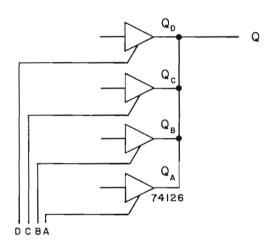

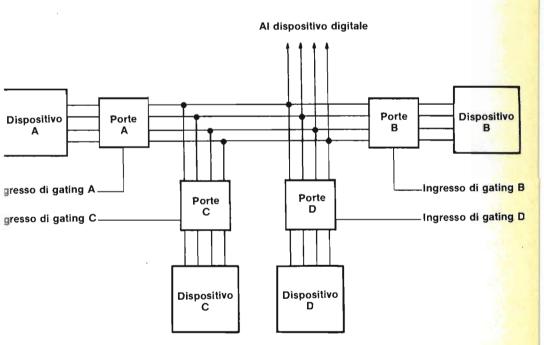

| CADI | TOLO 19 - LE TECNICHE DI BUS DATI NELL'USO DI DISPOSITIVI     |

| CAFI | THREE-STATE                                                   |

|      | THREE-STATE                                                   |

|      | Introduzione                                                  |

|      | Obiettivi                                                     |

|      | Che cosa è un bus?                                            |

|      | Bussing three-state                                           |

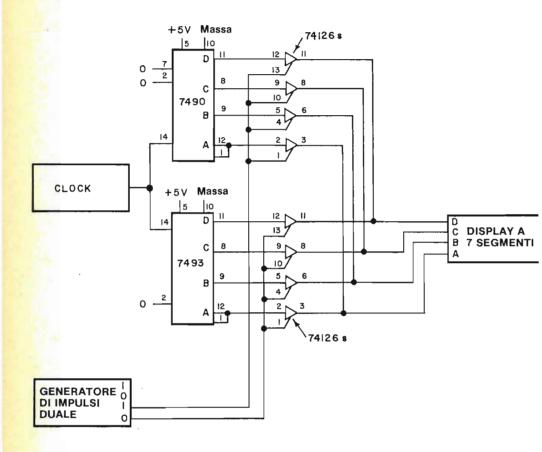

|      | Esempi di semplici sistemi bus                                |

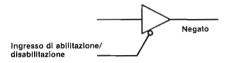

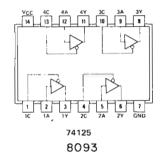

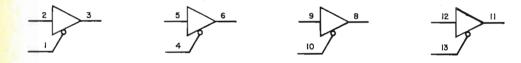

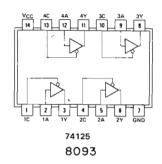

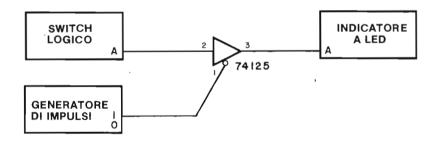

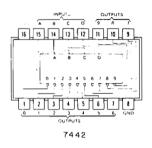

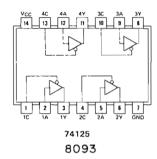

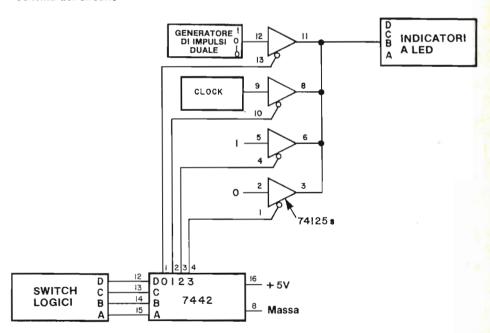

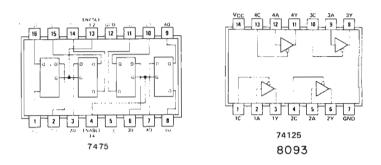

|      | Buffer three-state 74125                                      |

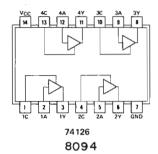

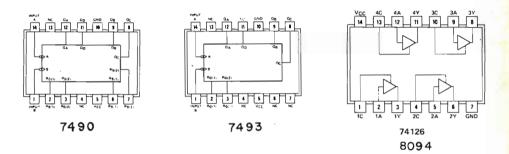

|      | Buffer three-state 74126                                      |

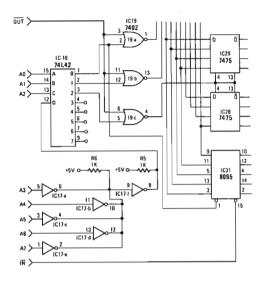

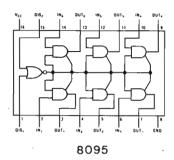

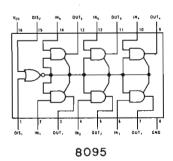

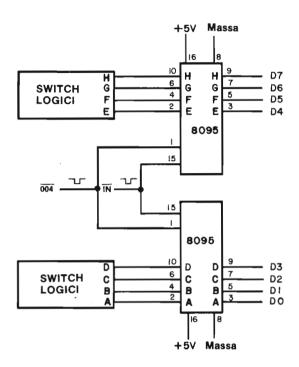

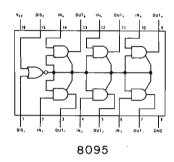

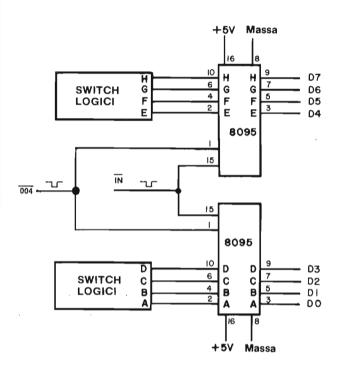

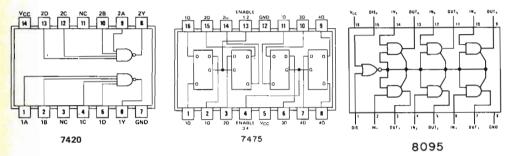

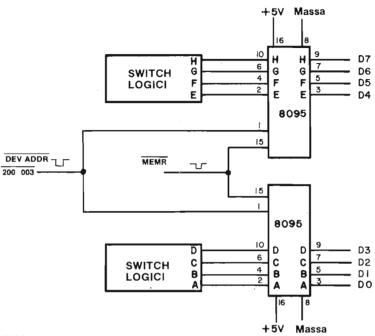

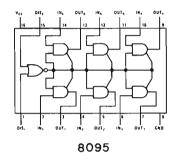

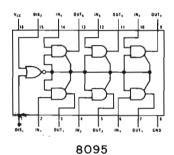

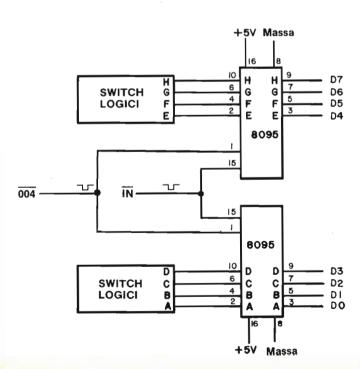

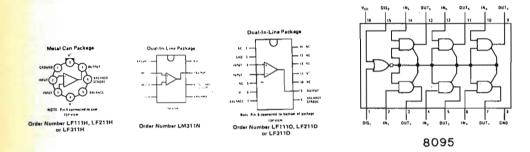

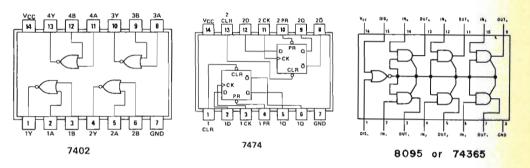

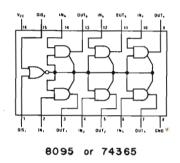

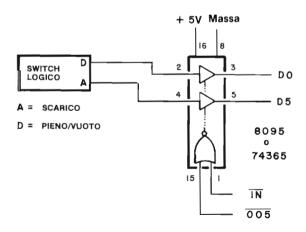

|      | Buffer three-state 8095                                       |

|      | Altri dispositivi three-state                                 |

|      |                                                               |

|      | Introduzione agli esperimenti                                 |

|      | Esperimento N. 1                                              |

|      | Esperimento N. 2                                              |

|      | Esperimento N. 3                                              |

|      | Esperimento N. 4                                              |

|      | Domande riepilogative                                         |

|      |                                                               |

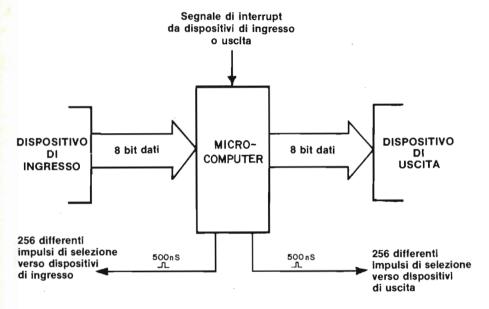

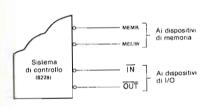

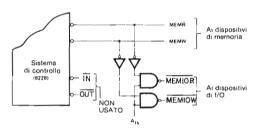

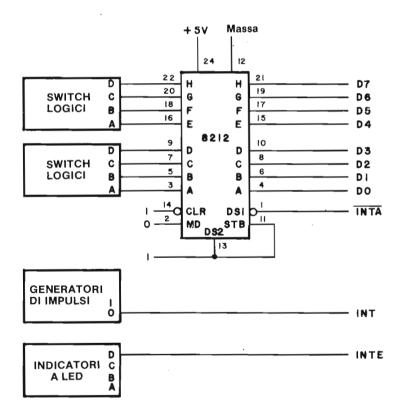

# CAPITOLO 20 - INTRODUZIONE ALLE TECNICHE DI I/O TRAMITE L'ACCUMULATORE

| Introduzione                                                            | 20-1  |

|-------------------------------------------------------------------------|-------|

| Objettivi                                                               | 20-1  |

| Obiettivi                                                               | 20-1  |

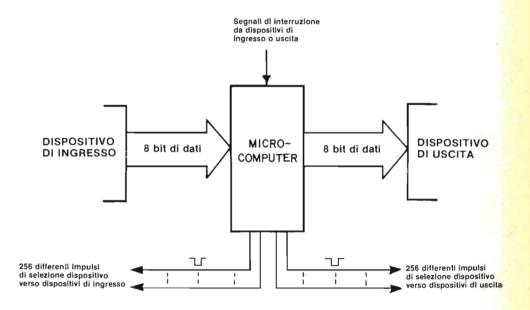

| Uscita del microcomputer                                                |       |

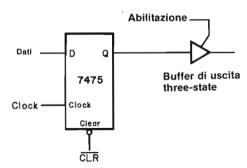

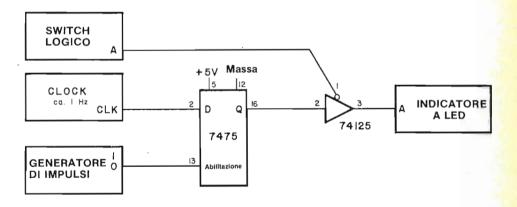

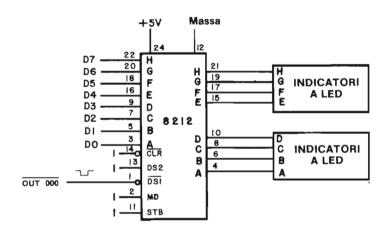

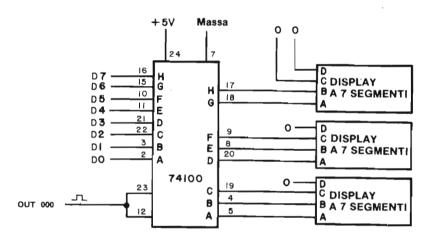

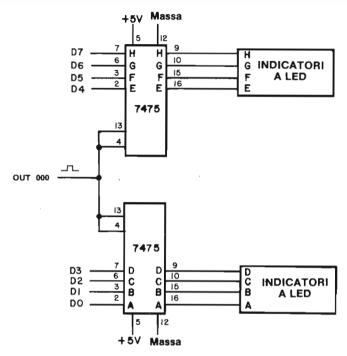

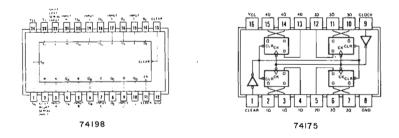

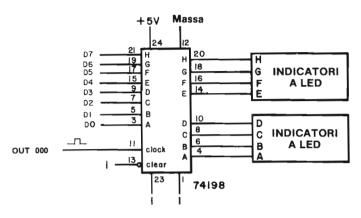

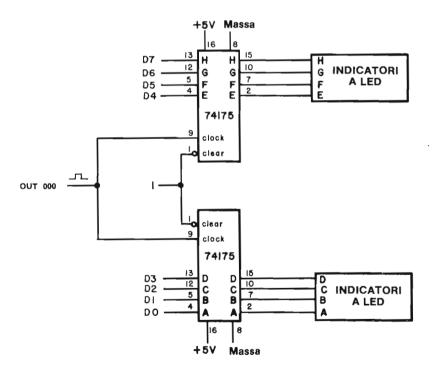

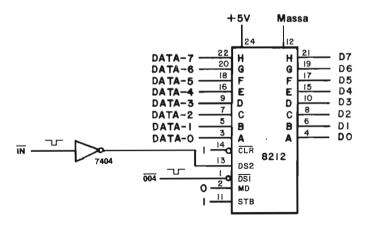

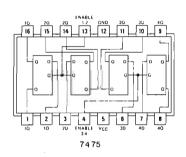

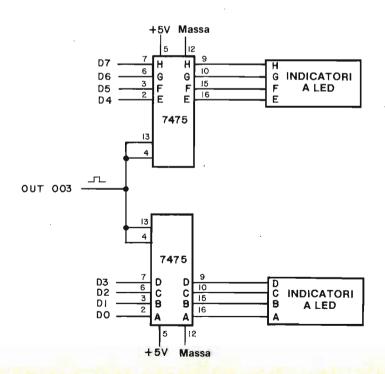

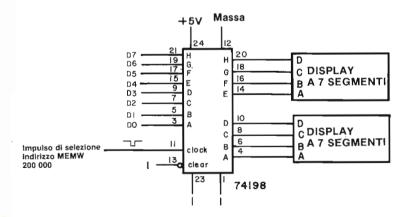

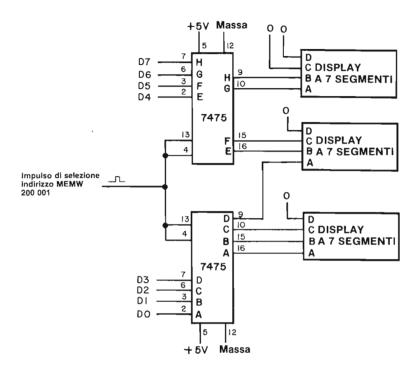

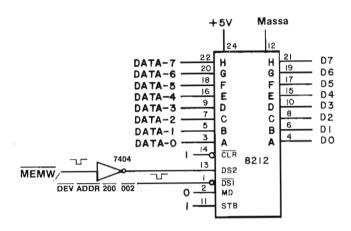

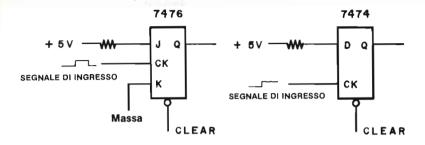

| Alguni girquiti di latch di uscita                                      | 20-6  |

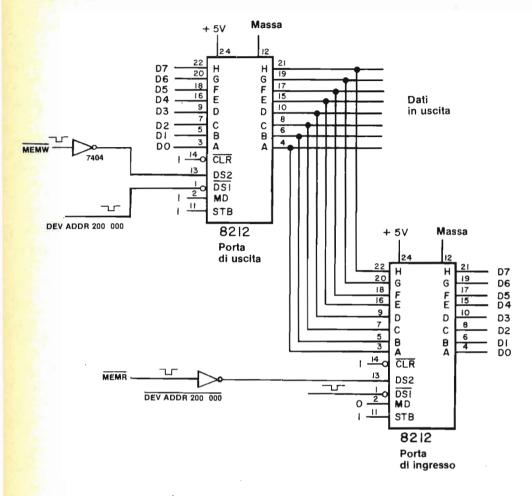

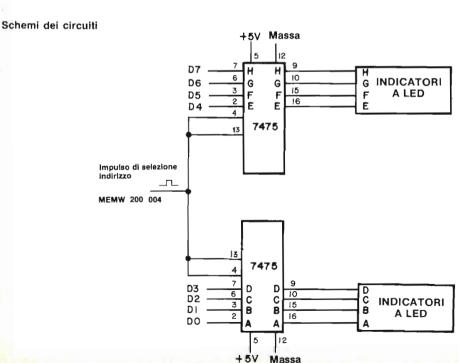

| Alcuni circuiti di latch di uscita                                      | 20-12 |

| Capacità di prioraggio in uscità                                        | 20-12 |

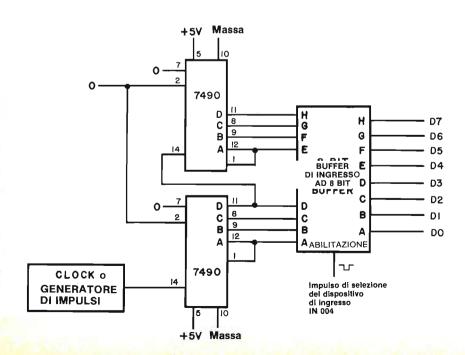

| Ingresso al microcomputer                                               |       |

|                                                                         | 20-15 |

| Istruzioni di I/O dell'accumulatore                                     |       |

| Primo programma di I/O                                                  | 20-15 |

| Secondo programma                                                       | 20-15 |

| Terzo programma                                                         |       |

| Quarto programma                                                        |       |

| Quinto programma                                                        | 20-10 |

| Introduzione agli esperimenti                                           | 20-20 |

| Esperimento N. 1                                                        | 20-21 |

| Esperimento N. 2                                                        | 20-26 |

| Esperimento N. 3                                                        | 20-33 |

| Domande riepilogative                                                   |       |

| Risposte                                                                | 20-40 |

|                                                                         |       |

| CAPITOLO 21 - INTRODUZIONE ALLE TECNICHE DI INGRESSO/USCITA             |       |

| MEMORY-MAPPED                                                           |       |

|                                                                         |       |

| Introduzione                                                            | 21-1  |

| Obiettivi                                                               | 21-1  |

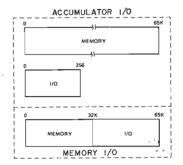

| I/O memory mapped e I/O tramite accumulatore                            | 21-2  |

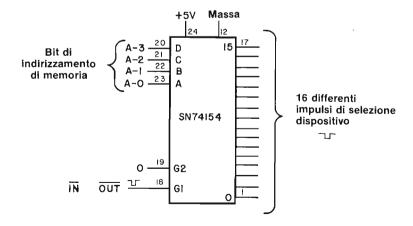

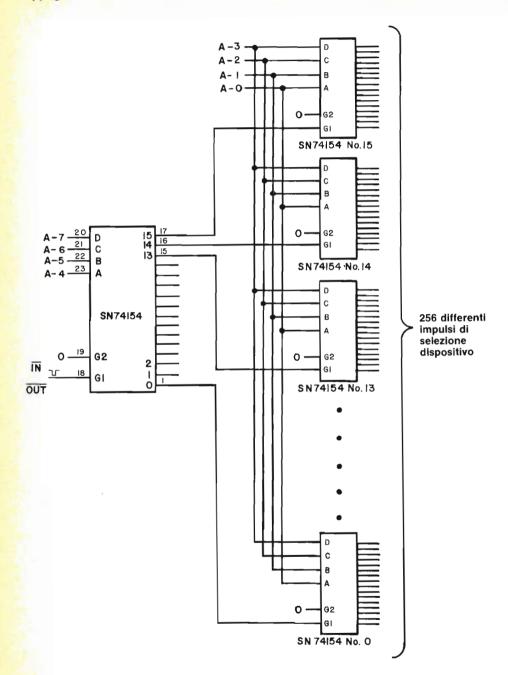

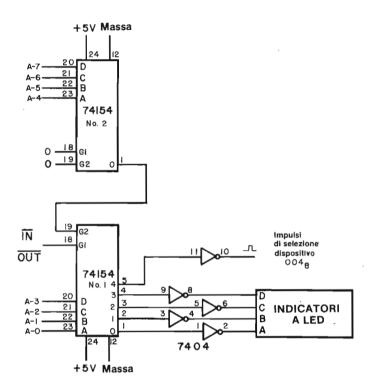

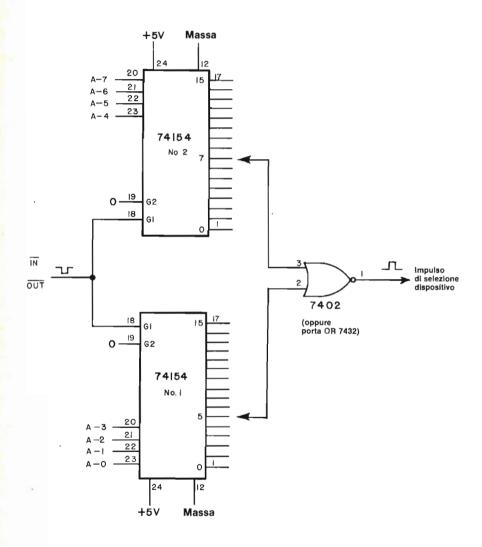

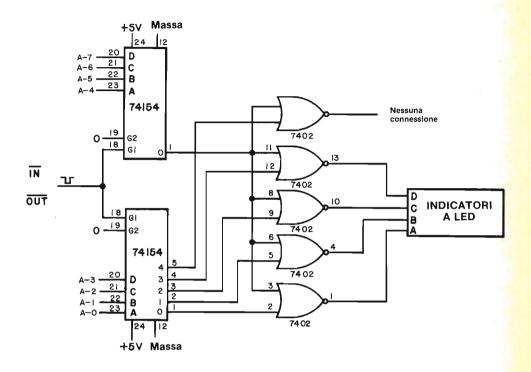

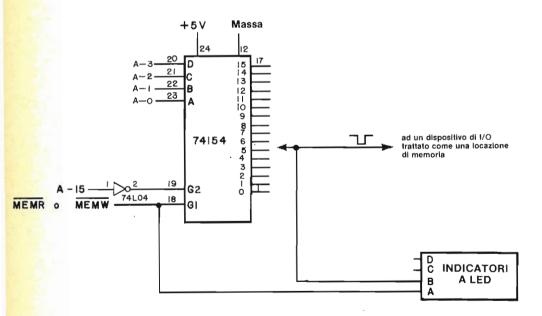

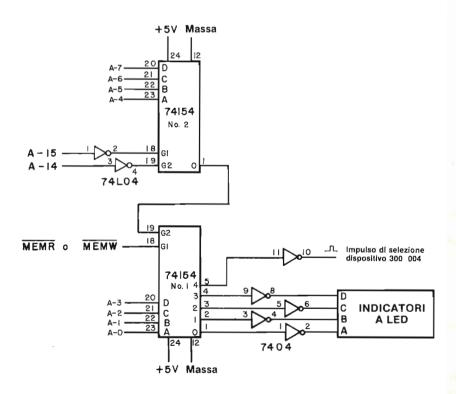

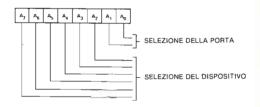

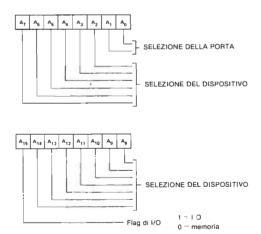

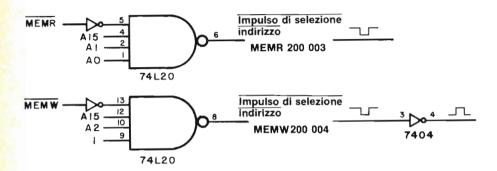

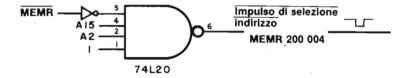

| Come si generano impulsi di selezione localizzati in mappa di memoria . | 21-3  |

| I/O memory mapped: uso del bit d'indirizzo A-15                         | 21-6  |

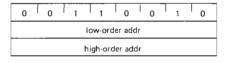

| Istruzioni di I/O memory mapped                                         | 21-8  |

| Istruzioni di I/O memory mapped                                         |       |

| di registri H                                                           | 21-8  |

| L'indirizzo della locazione di memoria M è contenuto nella coppia       |       |

| di registri B                                                           | 21-9  |

| L'indirizzo della locazione di memoria M è contenuto nella coppia       |       |

| di registri D                                                           | 21-9  |

| L'indirizzo della locazione di memoria M è contenuto nel secondo        |       |

| e nel terzo byte di istruzioni                                          | 21-10 |

| I cicli macchina memory read e memory write                             | 21-10 |

| l cicli macchina memory read e memory write                             | 21-11 |

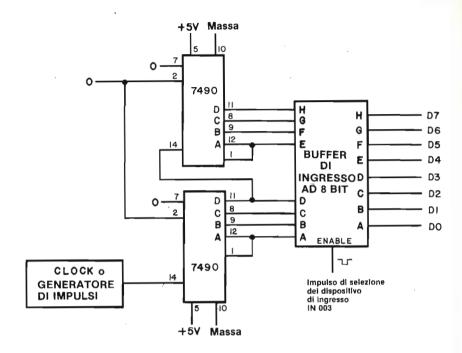

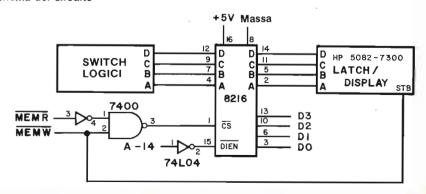

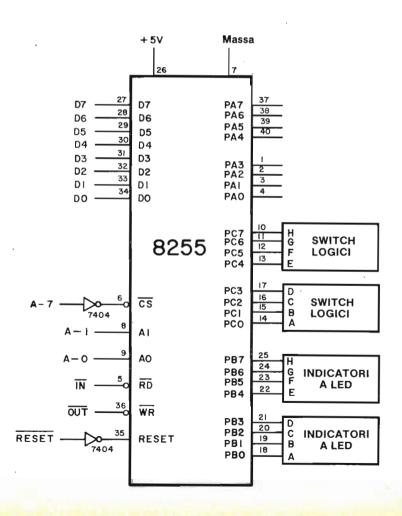

| Alcuni circuiti di ingresso/uscita                                      | 21-12 |

| Secondo programma                                                       | 21-14 |

| Terzo programma                                                         | 21-15 |

| Quarto programma                                                        | 21-15 |

| Quinto programma                                                        | 21-16 |

| Sesto programma                                                         | 21-17 |

| Settimo programma                                                       | 21-18 |

| Ottavo programma                                                        |       |

| Introduzione agli esperimenti                                           | 21-21 |

| Esperimento N. 1                                                        |       |

| Esperimento N. 2                                                        | 21-27 |

| Esperimento N. 3                                                        | 21-31 |

| Esperimento N. 4                                                        | 21-34 |

| Domande riepilogative                                                   | 21-37 |

| Risposte                                                                |       |

| CAPI | ITOLO 22 - L'INGRESSO/USCITA DEL MICROCOMPUTER: ALCUNI ESEMPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Introduzione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Obiettivi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | L'acquisizione dati con un microcomputer 8080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | Quanti canali dati?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | Memorizzazione a breve o a lungo termine?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Quante informazioni in un solo canale?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Che cosa fare dei dati acquisiti?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | Quanti canali al secondo?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | Primo programma: acquisizione di 64 canali di dati a 8 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Secondo programma: acquisizione lenta di canali dati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Terzo programma: uscita da un sistema di acquisizione dati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

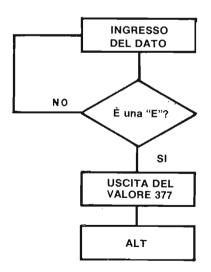

|      | Quarto programma: come si rivela un carattere ASCII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

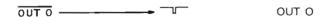

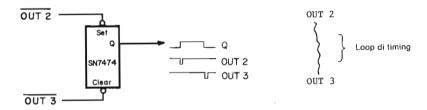

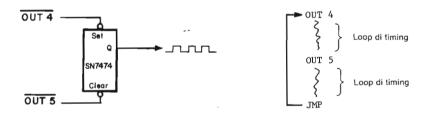

|      | Altri metodi per generare ritardi di tempo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Introduzione agli esperimenti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Esperimento N. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | Esperimento N. 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Esperimento N. 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Esperimento N. 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Esperimento N. 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Esperimento N. 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Domande riepilogative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Risposte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CAPI | ITOLO 23 - FLAG E INTERRUZIONI  Introduzione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Obiettivi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

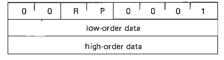

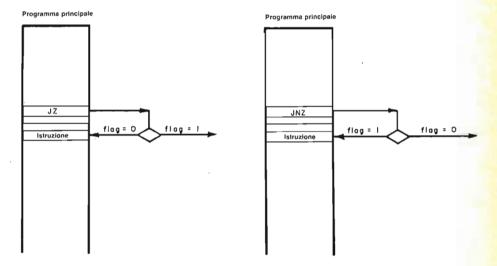

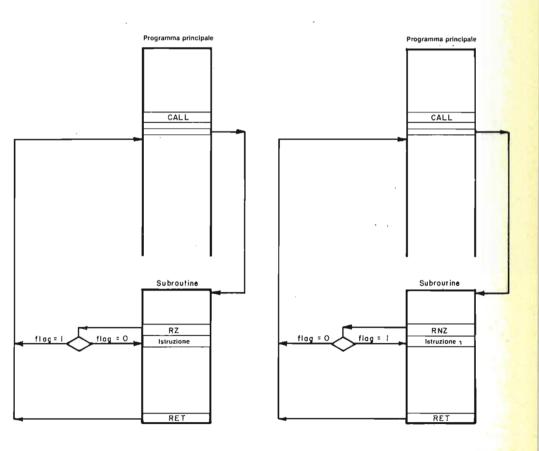

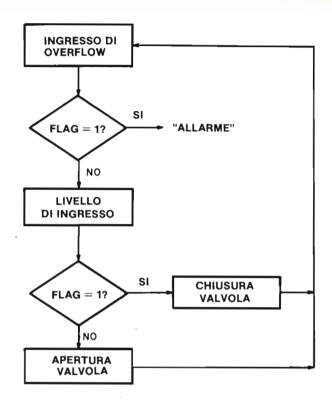

|      | Che cosa è un flag?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

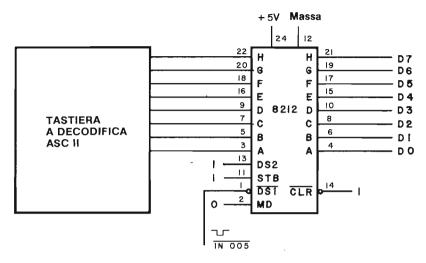

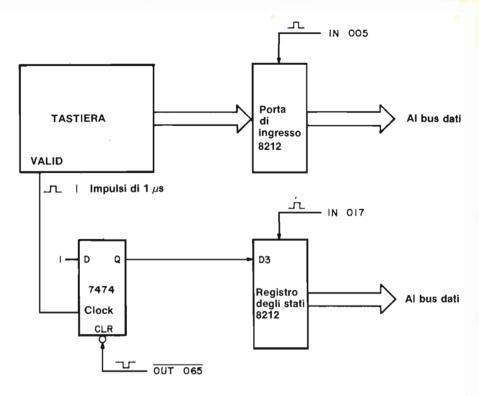

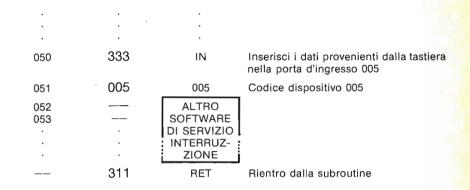

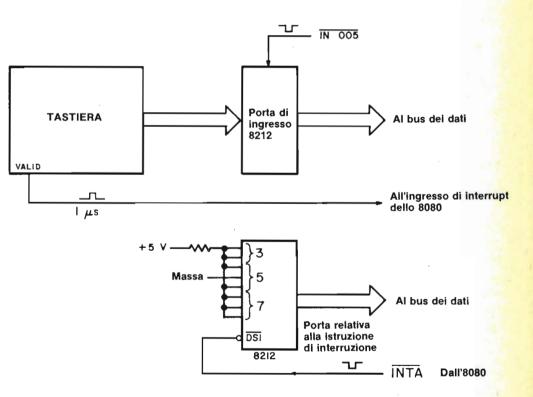

|      | Primo esempio: come si interfaccia una tastiera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

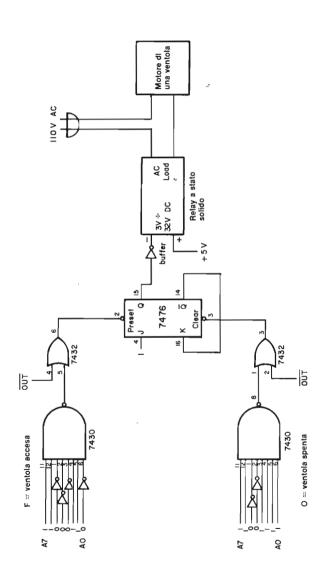

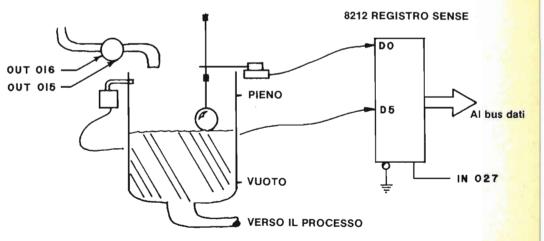

|      | Secondo esempio: controllo del livello di un solvente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | Operazione di interrogazione ciclica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

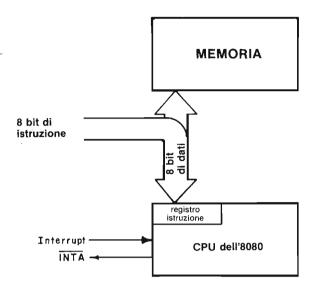

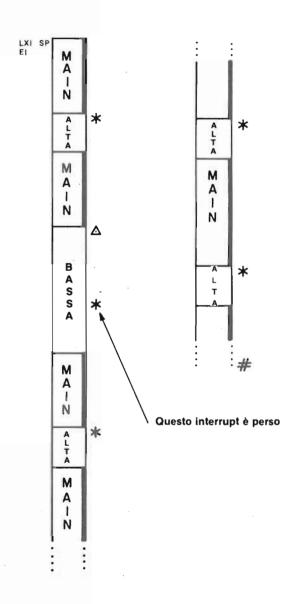

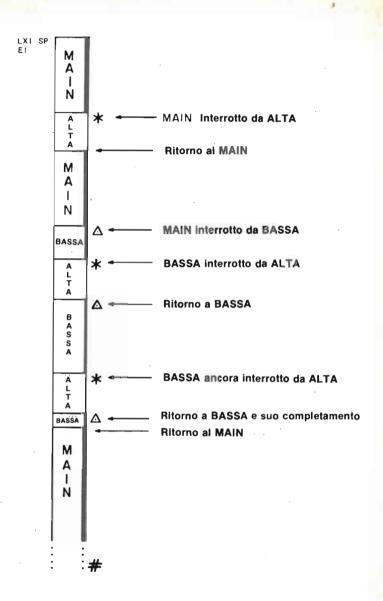

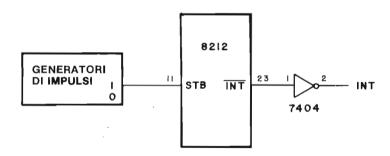

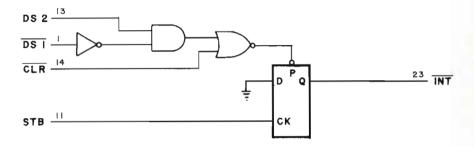

|      | Che cosa è un'interruzione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

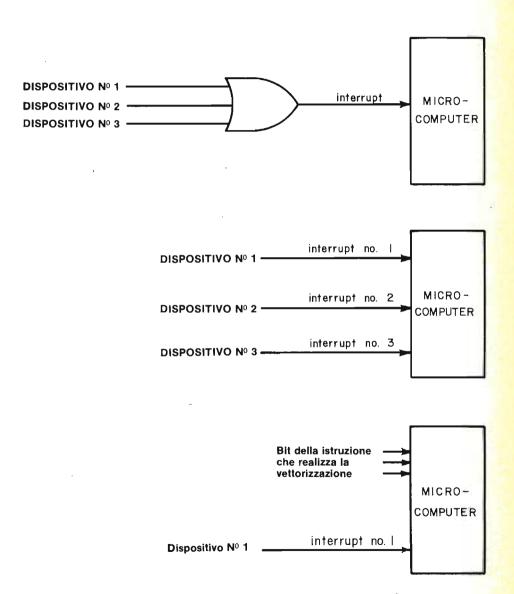

|      | Tipi di interruzione                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Ripristino: RST X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

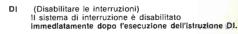

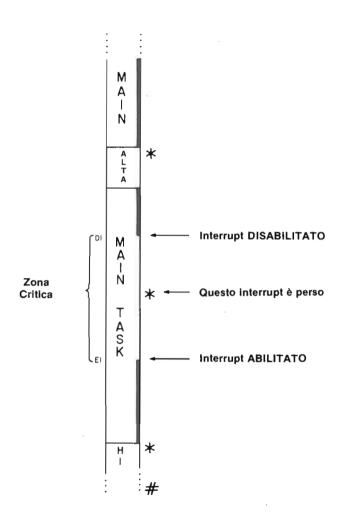

|      | Abilitazione e disabilitazione dell'interruzione: El e Dl 23-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

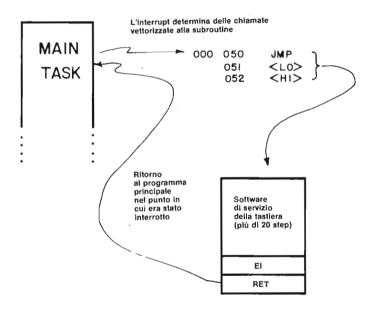

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

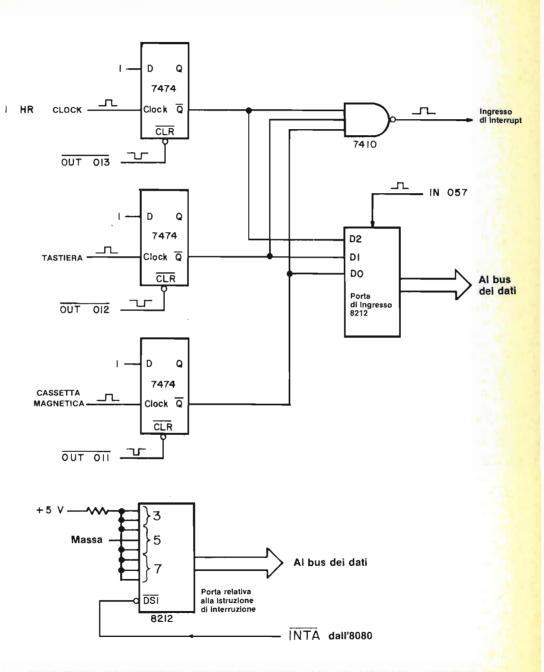

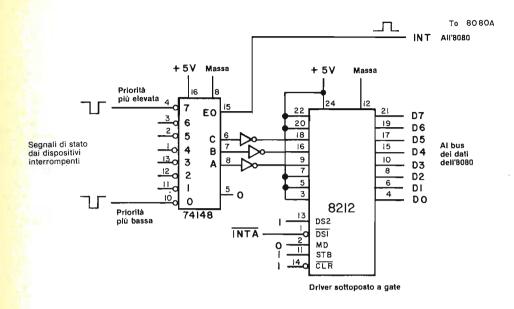

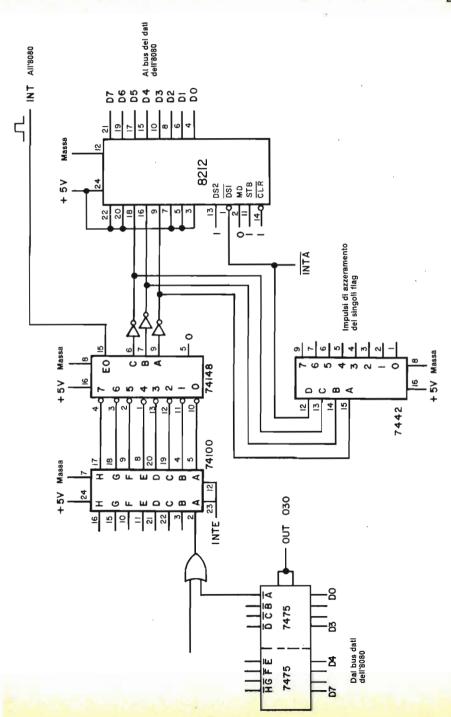

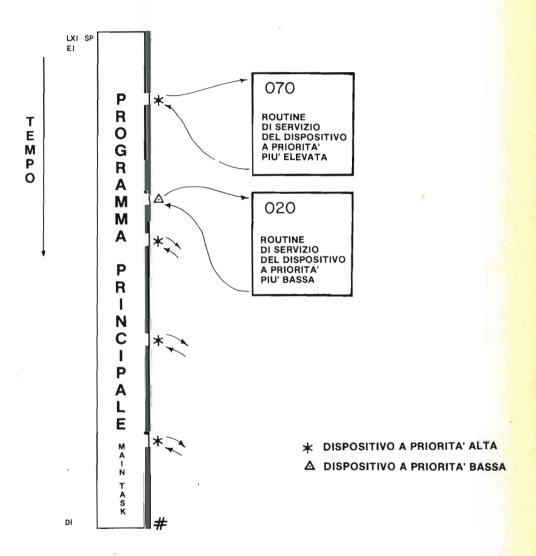

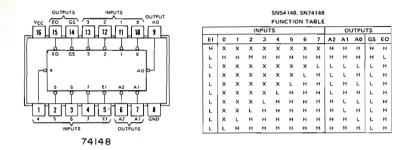

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità 23-1 Interruzioni con priorità da hardware 23-2 Il software di gestione delle interruzioni 23-2 Introduzione agli esperimenti 23-3 Esperimento N. 1 23-3 Esperimento N. 2 23-3 Esperimento N. 3 23-3 Esperimento N. 4 23-3 Esperimento N. 5 23-3 Esperimento N. 5 23-3 Esperimento N. 5 23-3                                                                                                                                                                                                                                                                                                                                                        |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera 23-1 Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera       23-1         Interruzioni con priorità                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera       23-1         Interruzioni con priorità       23-1         Interruzioni con priorità da hardware       23-2         Il software di gestione delle interruzioni       23-3         Introduzione agli esperimenti       23-3         Esperimento N. 1       23-3         Esperimento N. 2       23-3         Esperimento N. 3       23-3         Esperimento N. 4       23-3         Esperimento N. 5       23-4         Esperimento N. 6       23-4         Esperimento N. 7       23-4         Esperimento N. 8       23-5         Esperimento N. 9       23-5                                                                                                                |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera       23-1         Interruzioni con priorità       23-2         Interruzioni con priorità da hardware       23-2         Il software di gestione delle interruzioni       23-3         Introduzione agli esperimenti       23-3         Esperimento N. 1       23-3         Esperimento N. 2       23-3         Esperimento N. 3       23-3         Esperimento N. 4       23-3         Esperimento N. 5       23-4         Esperimento N. 6       23-4         Esperimento N. 7       23-4         Esperimento N. 8       23-5         Esperimento N. 9       23-5         Esperimento N. 10       23-6                                                                           |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera       23-1         Interruzioni con priorità       23-1         Interruzioni con priorità da hardware       23-2         Il software di gestione delle interruzioni       23-2         Introduzione agli esperimenti       23-3         Esperimento N. 1       23-3         Esperimento N. 2       23-3         Esperimento N. 3       23-3         Esperimento N. 5       23-4         Esperimento N. 5       23-4         Esperimento N. 6       23-4         Esperimento N. 7       23-4         Esperimento N. 8       23-5         Esperimento N. 9       23-5         Esperimento N. 10       23-6         Esperimento N. 11       23-6                                      |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera       23-1         Interruzioni con priorità       23-2         Interruzioni con priorità da hardware       23-2         Il software di gestione delle interruzioni       23-3         Introduzione agli esperimenti       23-3         Esperimento N. 1       23-3         Esperimento N. 2       23-3         Esperimento N. 3       23-3         Esperimento N. 4       23-3         Esperimento N. 5       23-4         Esperimento N. 6       23-4         Esperimento N. 7       23-4         Esperimento N. 8       23-5         Esperimento N. 9       23-5         Esperimento N. 10       23-6         Esperimento N. 11       23-6         Esperimento N. 12       23-7 |

|      | Terzo esempio: applicazione dell'interruzione all'interfaccia di una tastiera       23-1         Interruzioni con priorità       23-1         Interruzioni con priorità da hardware       23-2         Il software di gestione delle interruzioni       23-2         Introduzione agli esperimenti       23-3         Esperimento N. 1       23-3         Esperimento N. 2       23-3         Esperimento N. 3       23-3         Esperimento N. 5       23-4         Esperimento N. 5       23-4         Esperimento N. 6       23-4         Esperimento N. 7       23-4         Esperimento N. 8       23-5         Esperimento N. 9       23-5         Esperimento N. 10       23-6         Esperimento N. 11       23-6                                      |

## APPENDICI

| Appendice 1: Riferimenti                                                                                                                                                                                                                                                                                                                                                        | A-1                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Appendice 2: Dizionario dei termini usati nei Bugbooks V e VI                                                                                                                                                                                                                                                                                                                   | A-3                                                                                                          |

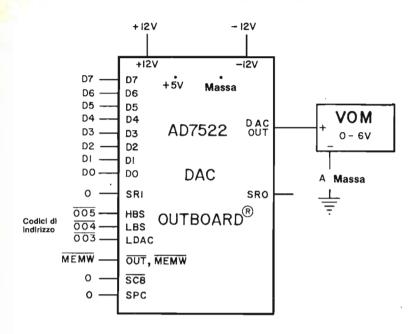

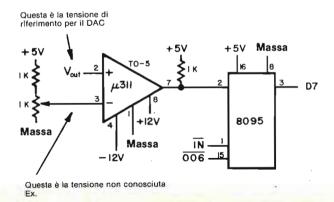

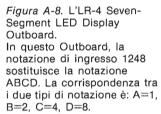

| Appendice 3: Outboards®                                                                                                                                                                                                                                                                                                                                                         | A-19                                                                                                         |

| Power Outboards                                                                                                                                                                                                                                                                                                                                                                 | A-19                                                                                                         |

| Logic Switch Outboards                                                                                                                                                                                                                                                                                                                                                          | A-22                                                                                                         |

| Led lamp monitor Outboards                                                                                                                                                                                                                                                                                                                                                      | A-23                                                                                                         |

| Pulser Outboards                                                                                                                                                                                                                                                                                                                                                                | A-23                                                                                                         |

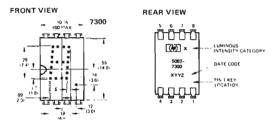

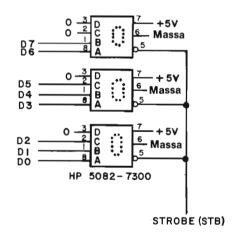

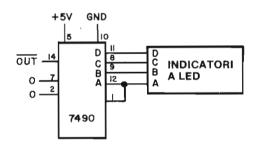

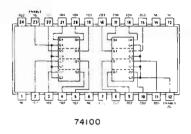

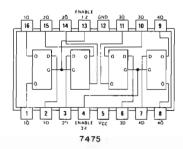

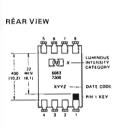

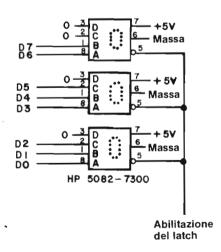

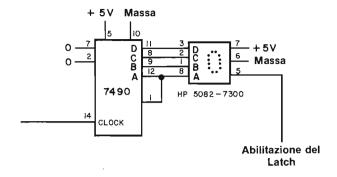

| Display e latch/display Outboards                                                                                                                                                                                                                                                                                                                                               | A-24                                                                                                         |

| Clock Outboards                                                                                                                                                                                                                                                                                                                                                                 | A-27                                                                                                         |

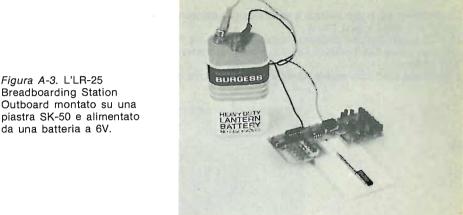

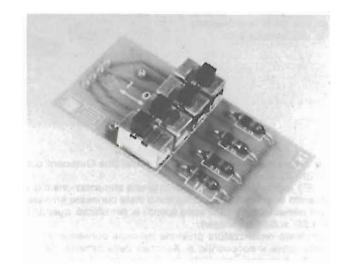

| Breadboarding station Outboard                                                                                                                                                                                                                                                                                                                                                  | A-27                                                                                                         |

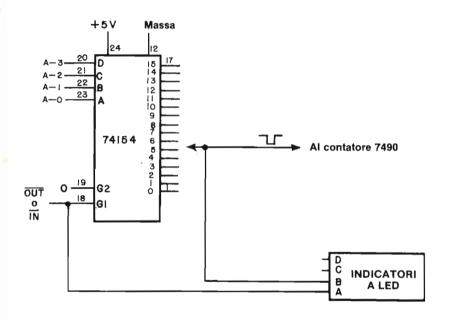

| Decoder Outboard                                                                                                                                                                                                                                                                                                                                                                | A-30                                                                                                         |

| Monostable Outboard                                                                                                                                                                                                                                                                                                                                                             | A-30                                                                                                         |

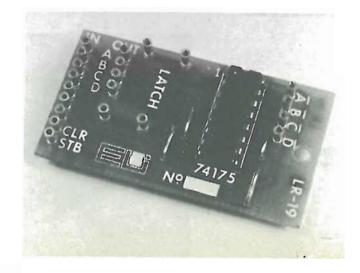

| Latch Outboard                                                                                                                                                                                                                                                                                                                                                                  | A-30                                                                                                         |

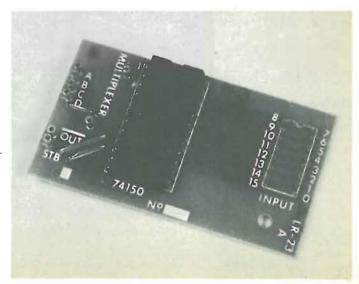

| Multiplexer Outboard                                                                                                                                                                                                                                                                                                                                                            | A-31                                                                                                         |

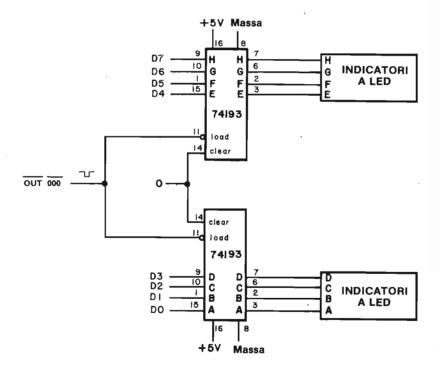

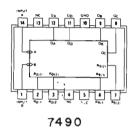

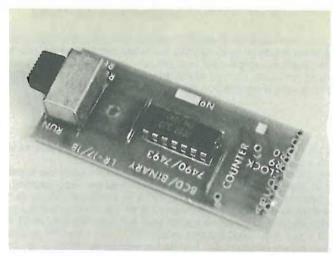

| Counter Outboards                                                                                                                                                                                                                                                                                                                                                               | A-31                                                                                                         |

| Driver/inverter/NOR Outboard                                                                                                                                                                                                                                                                                                                                                    | A-31                                                                                                         |

| Universal asynchronous receiver/transmitter Outboard                                                                                                                                                                                                                                                                                                                            | A-33                                                                                                         |

| TTL/RS - 232C Interface Outboard                                                                                                                                                                                                                                                                                                                                                | A-33                                                                                                         |

| Programmable timer Outboard                                                                                                                                                                                                                                                                                                                                                     | A-35                                                                                                         |

| Appendice 4: Tabella di conversione fra codici ottali e codici esadecimali                                                                                                                                                                                                                                                                                                      | A-36                                                                                                         |

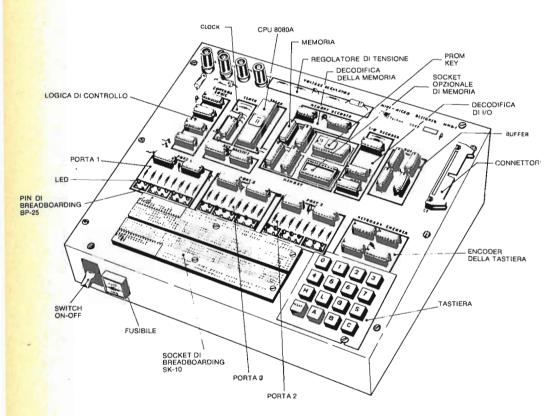

| Appendice 5: Descrizione del microcomputer MMD-1                                                                                                                                                                                                                                                                                                                                | A-37                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

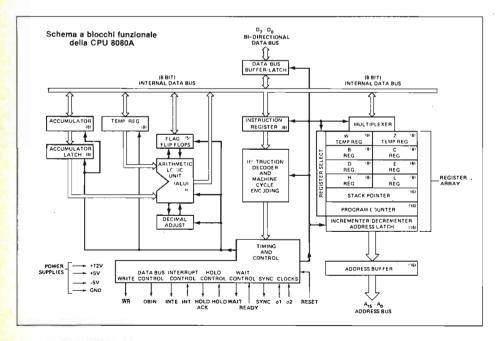

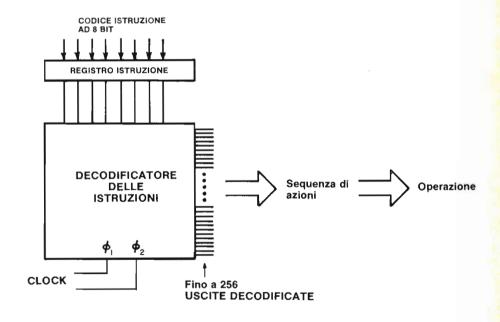

| Introduzione                                                                                                                                                                                                                                                                                                                                                                    | A-37                                                                                                         |

| Introduzione                                                                                                                                                                                                                                                                                                                                                                    | A-37<br>A-37                                                                                                 |

| Introduzione                                                                                                                                                                                                                                                                                                                                                                    | A-37<br>A-37<br>A-38                                                                                         |

| Introduzione                                                                                                                                                                                                                                                                                                                                                                    | A-37<br>A-37<br>A-38<br>A-40                                                                                 |

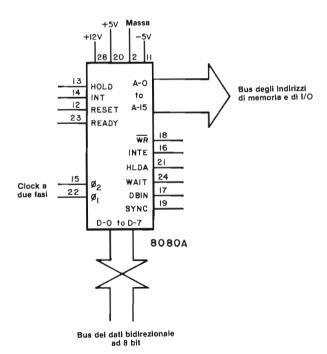

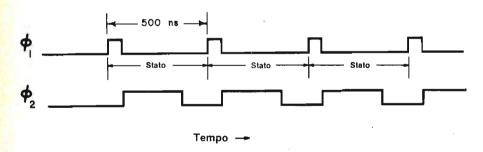

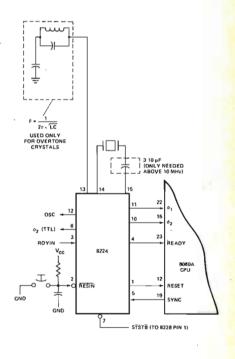

| Introduzione Obiettivi Il microprocessore 8080 Alimentazione Ingressi di clock                                                                                                                                                                                                                                                                                                  | A-37<br>A-37<br>A-38<br>A-40<br>A-40                                                                         |

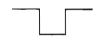

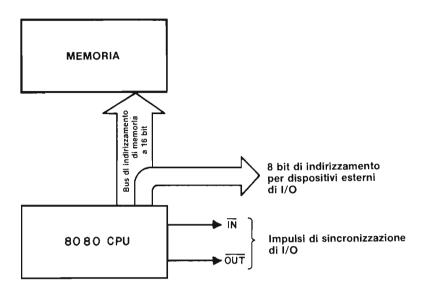

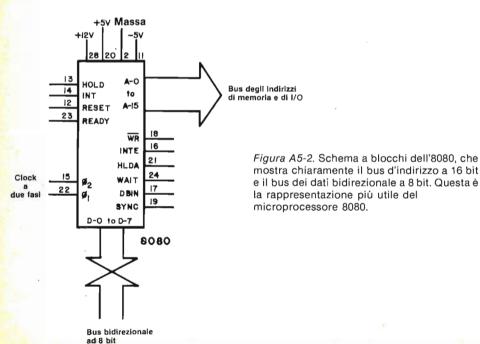

| Introduzione Obiettivi Il microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria                                                                                                                                                                                                                                                                   | A-37<br>A-37<br>A-38<br>A-40<br>A-40<br>A-41                                                                 |

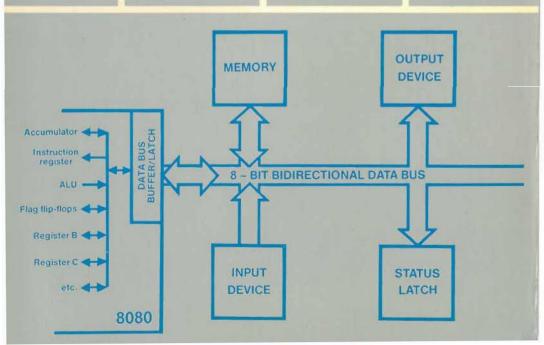

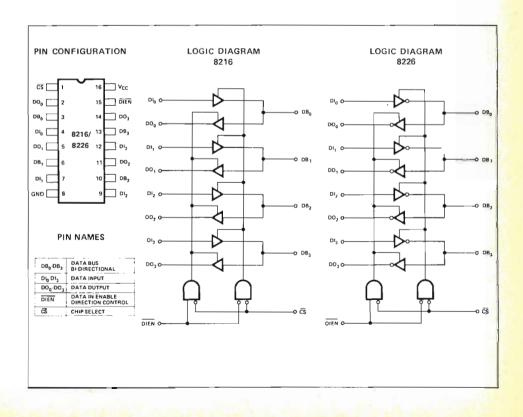

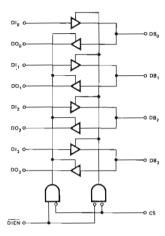

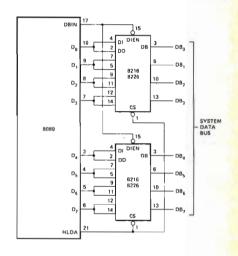

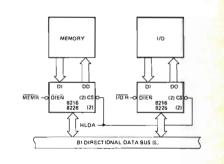

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale                                                                                                                                                                                                                                         | A-37<br>A-37<br>A-38<br>A-40<br>A-41<br>A-41                                                                 |

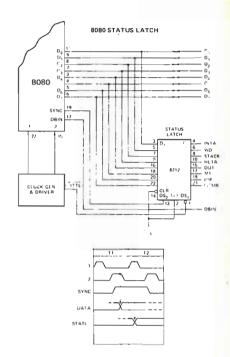

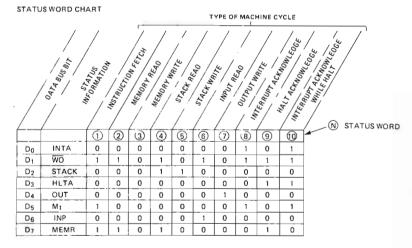

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo                                                                                                                                                                                                                    | A-37<br>A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-41                                                         |

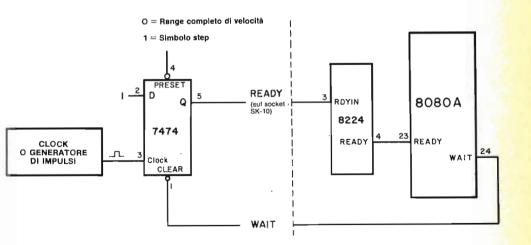

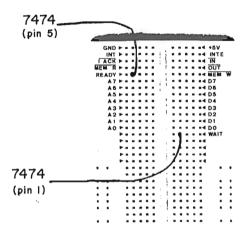

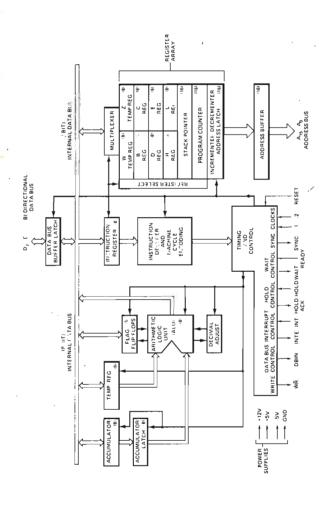

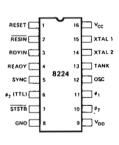

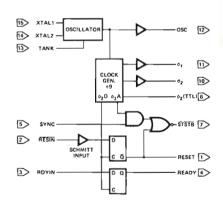

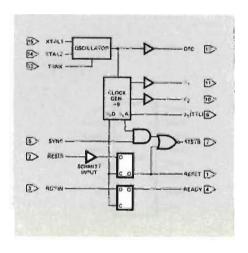

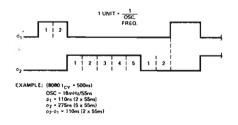

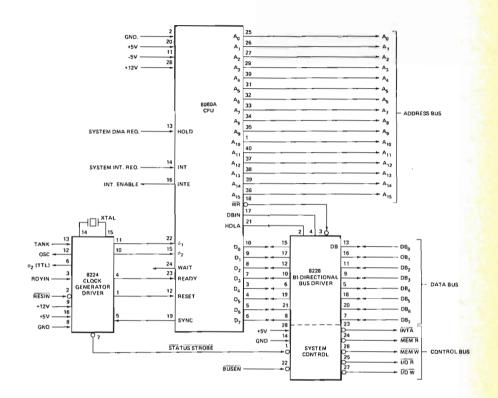

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224                                                                                                                                                                                        | A-37<br>A-38<br>A-40<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44                                                 |

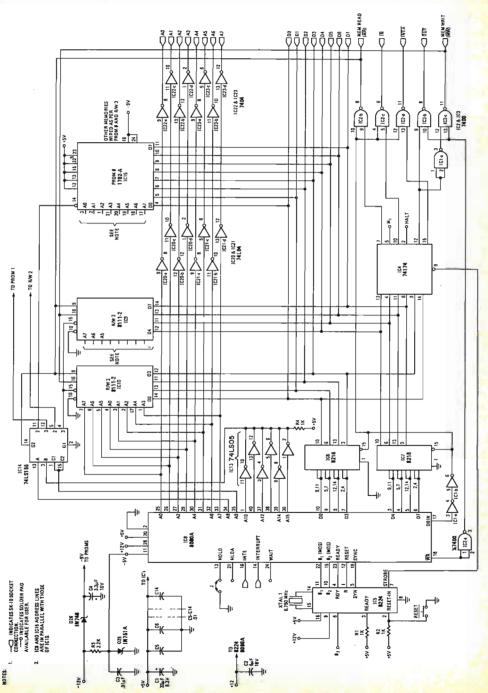

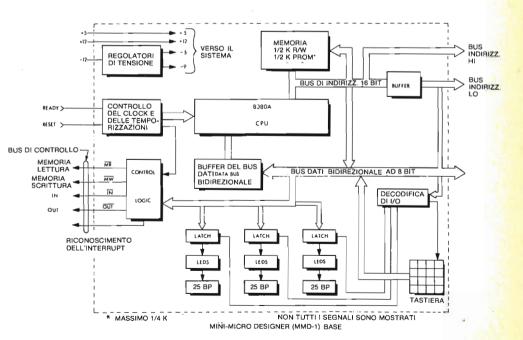

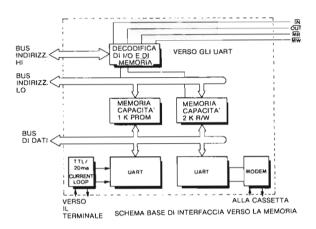

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1                                                                                                                                                                 | A-37<br>A-38<br>A-40<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48                                         |

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione                                                                                                                                                   | A-37<br>A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48                                 |

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A                                                                                                                             | A-37<br>A-38<br>A-40<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48                                 |

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo                                                                                                          | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48<br>A-50                                 |

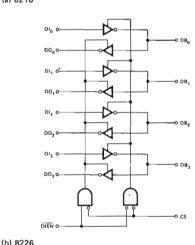

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo Bus driver                                                                                               | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48<br>A-50<br>A-50                         |

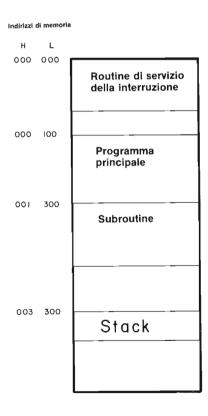

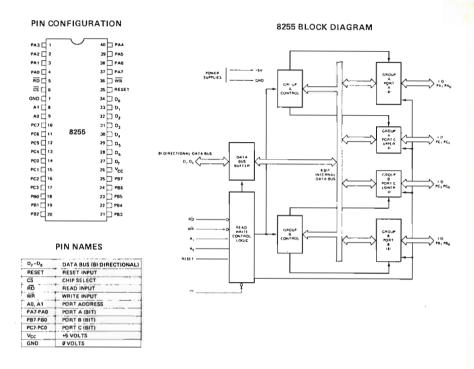

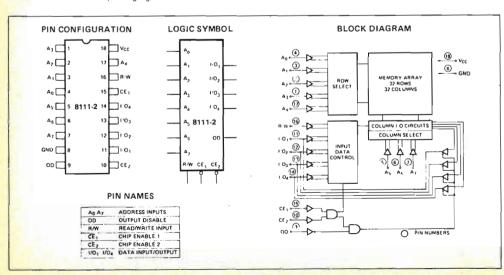

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo Bus driver Memoria                                                                                       | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-48<br>A-48<br>A-50<br>A-50<br>A-56                         |

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo Bus driver Memoria I bus del microcomputer MMD-1                                                         | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48<br>A-50<br>A-50<br>A-56<br>A-61         |

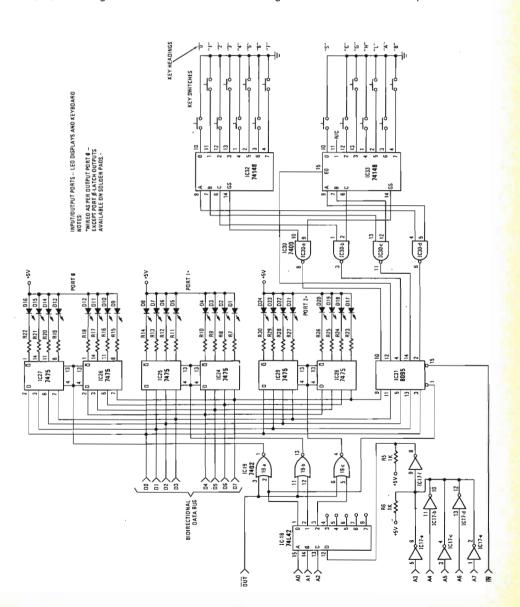

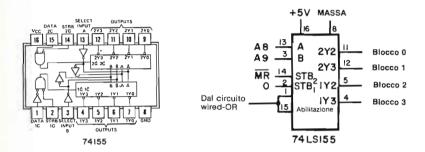

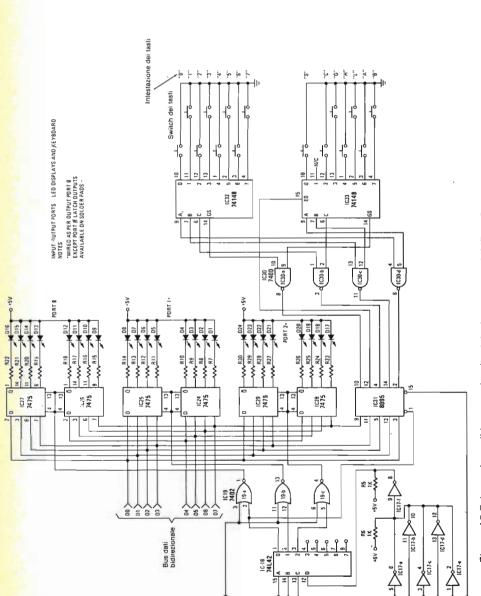

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo Bus driver Memoria I bus del microcomputer MMD-1 Ingresso/Uscita                                         | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48<br>A-50<br>A-50<br>A-61<br>A-61         |

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo Bus driver Memoria I bus del microcomputer MMD-1 Ingresso/Uscita Microcomputer MMD-1: II sistema globale | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-50<br>A-50<br>A-56<br>A-61<br>A-61<br>A-63 |

| Introduzione Obiettivi II microprocessore 8080 Alimentazione Ingressi di clock Bus degli indirizzi di memoria Bus di dati bidirezionale Segnali di controllo Clock generator/driver 8224 II microcomputer MMD-1 Alimentazione Microprocessore 8080A Linee di controllo Bus driver Memoria I bus del microcomputer MMD-1 Ingresso/Uscita                                         | A-37<br>A-38<br>A-40<br>A-41<br>A-41<br>A-42<br>A-44<br>A-48<br>A-48<br>A-50<br>A-50<br>A-61<br>A-61         |

Le informazioni contenute in questo libro sono state scrupolosamente controllate e sono perciò completamente attendibili. Tuttavia non si assume alcuna responsabilità per eventuali inesattezze. Tali informazioni inoltre, non danno diritto alla fabbricazione di prodotti brevettati della E. & L. Instruments, Inc. o da altri. La E. & L. Instruments, Inc. si riserva i diritti di modificare le specifiche in qualsiasi momento senza preavviso.

## **PREFAZIONE**

Benvenuti nella nuova rivoluzione elettronica. In 10 anni la tecnologia dei circuiti elettronici ha trasformato i circuiti integrati digitali da costosi componenti per semplici funzioni logiche, a componenti ad alta complessività, contenenti fino a 10.000 transistor. Da questa rivoluzione è nato il computer-su-singolo-chip! Questo nuovo componente contiene tutto quello che è richiesto da un computer digitale (unità centrale, memoria a lettura/scrittura, memoria ROM, circuiteria di interfaccia). Fra pochi anni sarete in grado di acquistare una manciata di questi componenti a prezzi impensabili. Si ritiene che attualmente esista circa un miliardo di microcomputer in circolazione. Una rivoluzione nel campo dei computer? Sicuramente.

Nell'istruzione poi, pensiamo che la nuova rivoluzione elettronica creerà importanti cambiamenti ed opportunità: